#### © 2002 Seth Copen Goldstein

Micro-35

© 2002 Seth Copen Goldstein

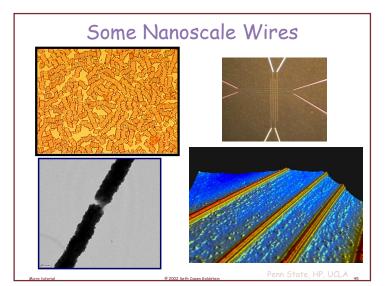

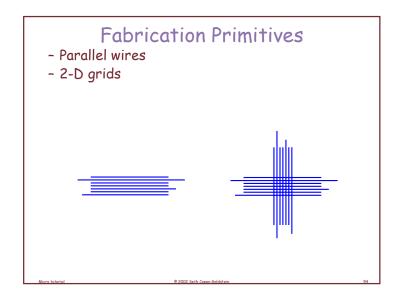

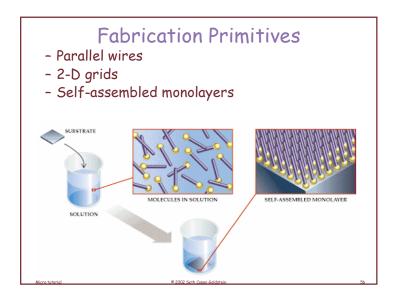

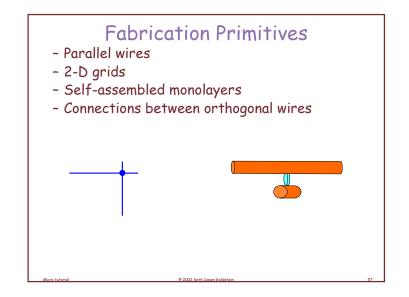

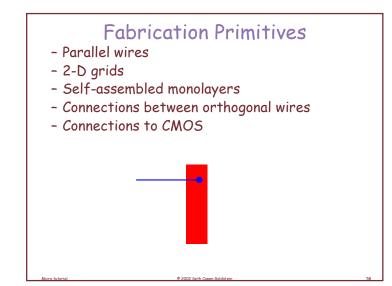

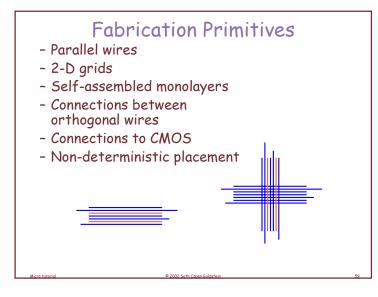

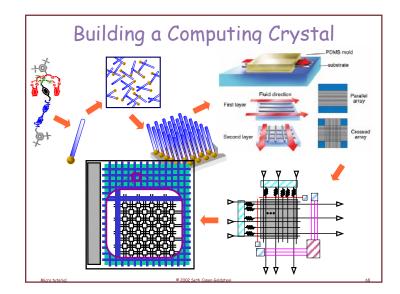

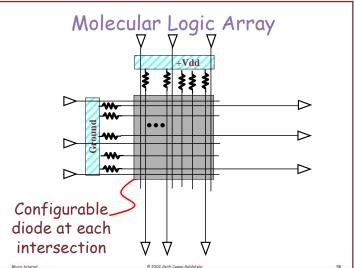

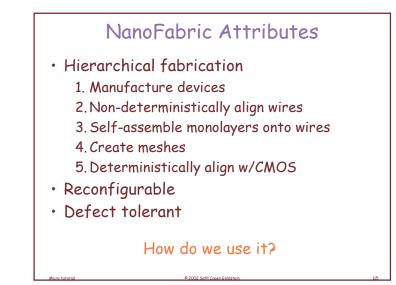

## **Fabrication Primitives**

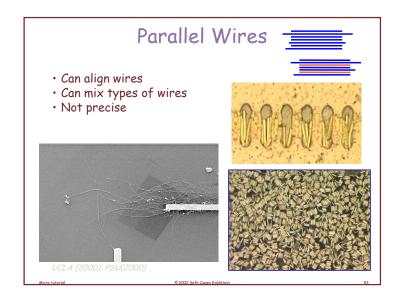

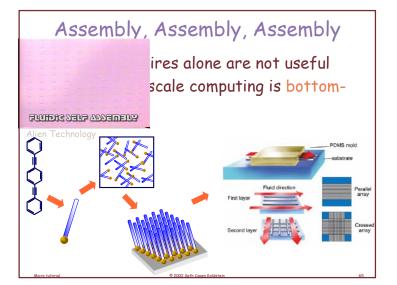

- Parallel wires

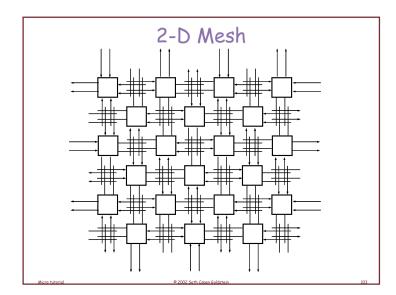

- 2-D grids

- Self-assembled monolayers

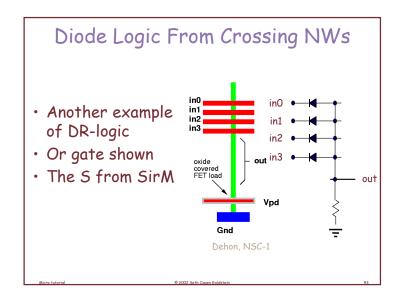

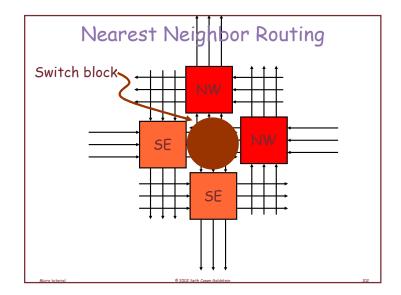

- Connections between orthogonal wires

- Connections to CMOS

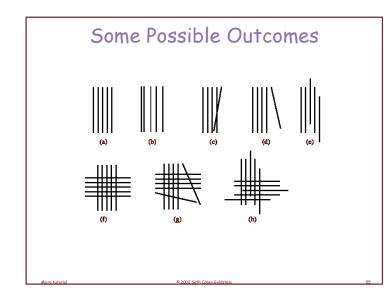

- Non-deterministic placement

- Selective variability on a lithographic scale

Micro-35

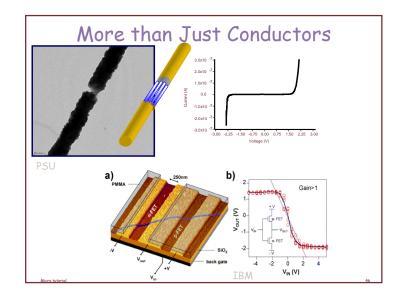

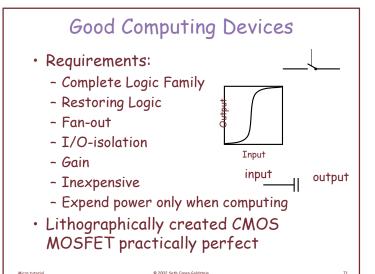

| Requirements: Nano-                                   |           |

|-------------------------------------------------------|-----------|

| <ul> <li>Complete logic family</li> </ul>             | CMOS Nano |

| <ul> <li>Composable Circuits</li> <li>Gain</li> </ul> |           |

| - Input/Output isolation<br>- Fan-out                 |           |

| <ul> <li>Fabrication friendly</li> </ul>              |           |

| <ul> <li>Low variability</li> </ul>                   |           |

| <ul> <li>Device/Wire ratio</li> </ul>                 |           |

| <ul> <li>Energy-Delay product</li> </ul>              | <b>.</b>  |

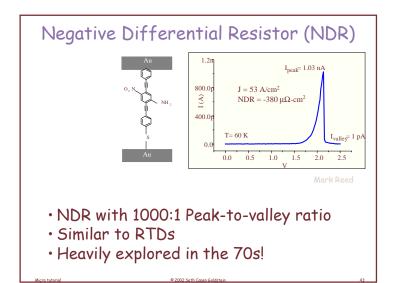

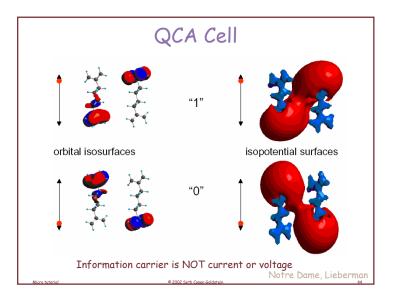

| <ul> <li>Harness Novel IV curves</li> </ul>           | 😕 😊       |

|                                                       |           |

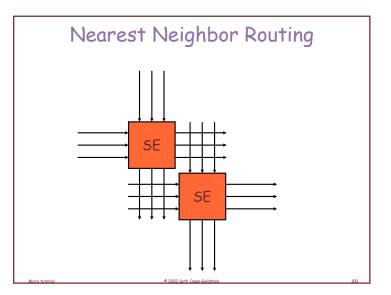

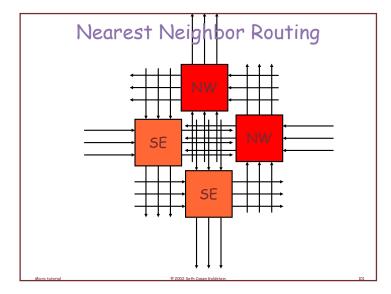

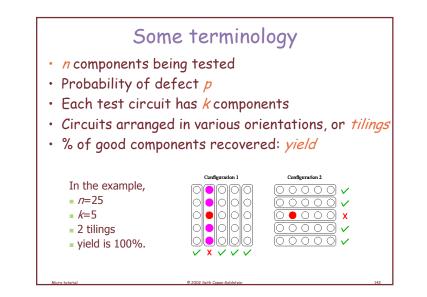

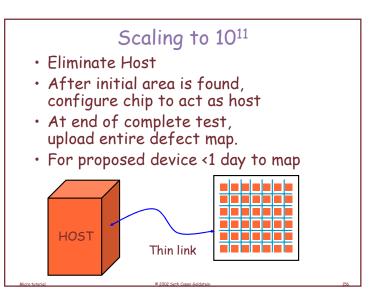

### Assumptions (cont.)

- Arbitrary, unlimited connectivity

- any component can be connected to any other, including non-adjacent ones

- makes large number of tilings possible

- Above assumption: to simplify analysis

# Assumptions

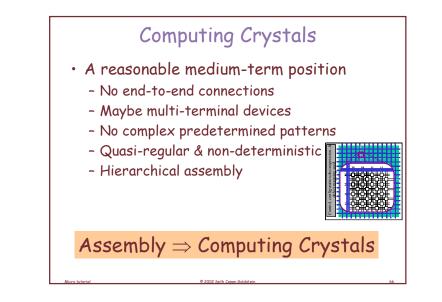

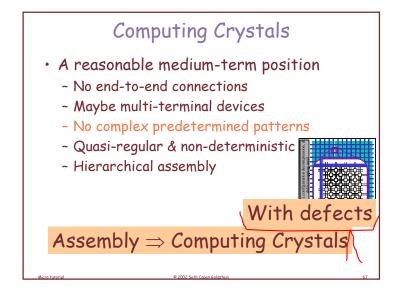

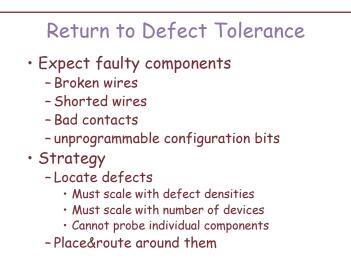

- Permanent defects

- defective component always displays faulty behavior

- defect in one component does not affect others

- i.e., no short-circuits between wires

- $\boldsymbol{\cdot}$  manufacturing process biased to ensure this

- no Byzantine failures

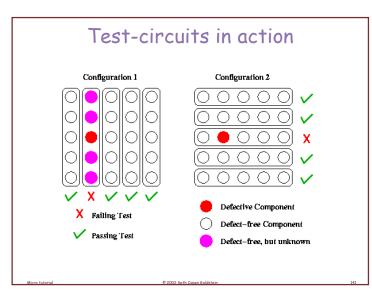

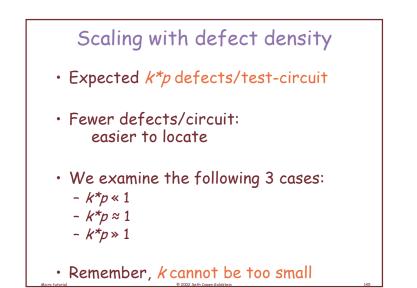

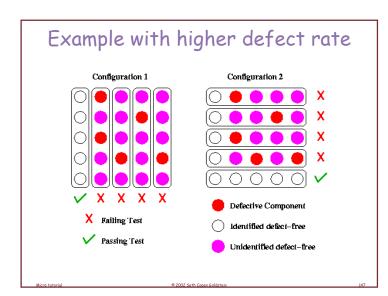

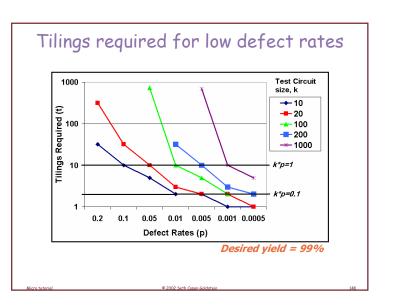

## High defect rates: *k\*p* » 1

- Many defects/test-circuit

- Finding a defect free circuit is extremely unlikely

- e.g., for k=100, p=0.1, probability of finding a defect-free circuit =  $1.76^{\ast}10^{-5}$

- The previous approach does not work: something new is needed

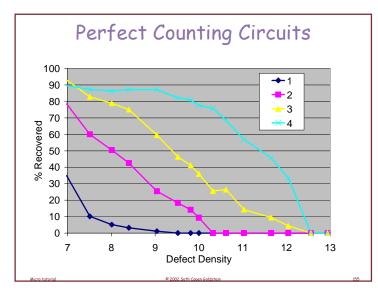

#### Making test circuits more powerful

- Use test-circuits which *count* defects

- error in output depends directly on number of defects

- e.g., use error-correcting, fault-tolerant circuit designs

- These can return correct counts only upto a certain threshold

- must indicate when threshold is crossed

- use two different test circuits simultaneously!

# New testing methodology

- Split into two phases:

- probability-assignment phase

- defect-location phase

- First phase: identifies components with high probability of being defect-free

- Second phase: tests these components further to pin-point defects

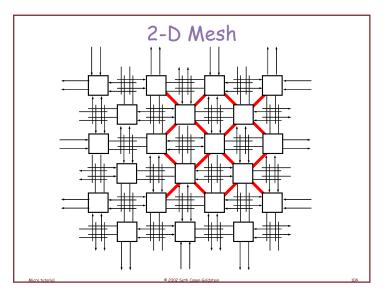

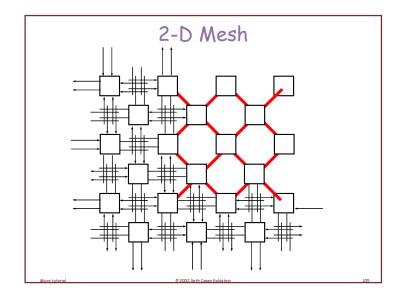

- each phase: uses many different tilings

# Probability-assignment phase

- Each component made a part of many different test circuits and defect counts are obtained

- Find probability of each component being good using Bayesian probabilistic analysis

- Discard components with low probability of being good

### This works, but why?

- Intuitively, a defective component increases defect counts of all circuits it is a part of

- If a component is part of many circuits with a high defect count, our analysis assigns it a low probability of being good

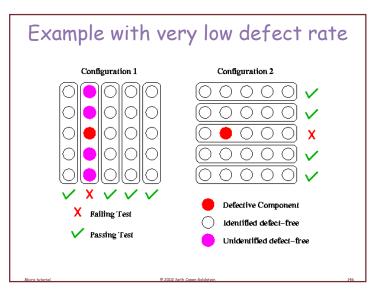

## Defect location phase

- Remaining components have low defect rate

- Configure into test circuits, mark all the components good if circuit has no defects

- Repeat for many different tilings

- Everything left is marked bad

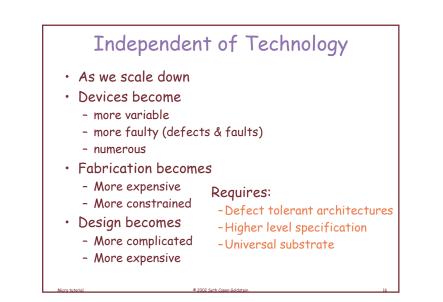

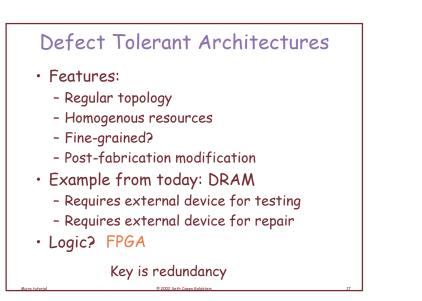

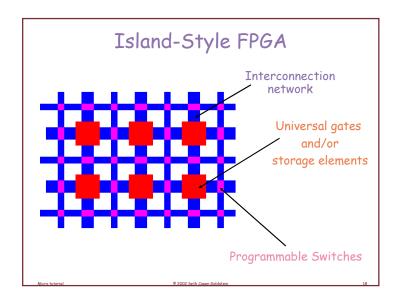

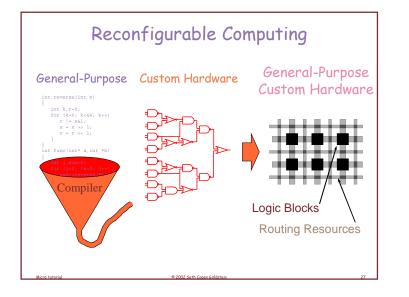

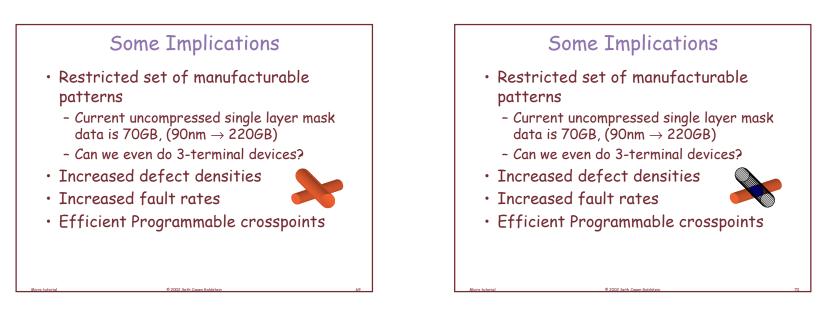

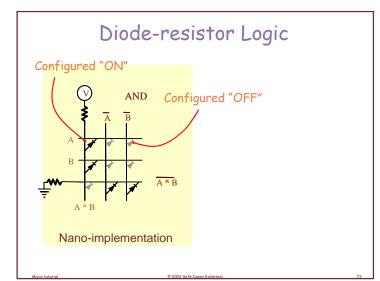

| <ul> <li>Significant progress in nanoscale</li> <li>Devices</li> <li>Wires</li> <li>Fabrication</li> <li>Independent of Technology</li> </ul>                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Loss of arbitrary patterns at fab time</li> <li>Increase in defects and faults</li> <li>Reconfigurable fabrics look good</li> <li>Molecular electronics is reconfigurable</li> </ul> |

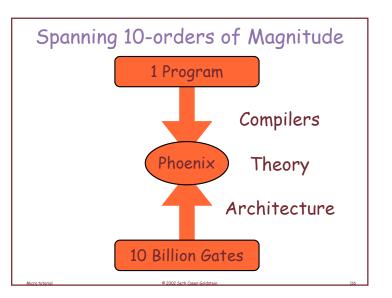

# Plenty of Interesting Research

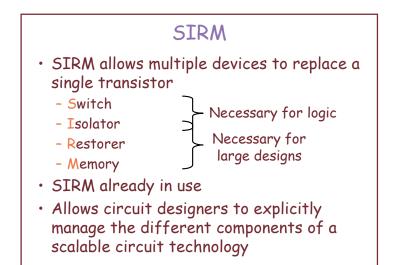

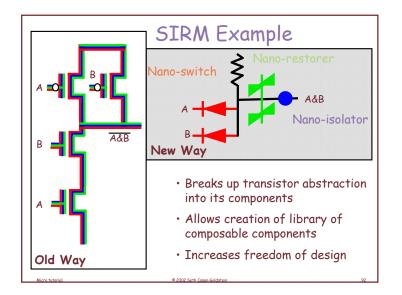

- Devices Abstractions

- Circuits

- Architectures

- Cad Tools

- Compilers

- Defect Tolerance

- Fault Tolerance